英特尔押注全新堆叠叉片式晶体管技术,目标2nm

继三星和台积电之后,英特尔也开始2nm工艺上的突破。

近日,网络上的一项专利,暗示了这家芯片巨头或借助“堆叠叉片式”晶体管技术来延续摩尔定律,并且用于2nm及以下先进制程的半导体工艺上。

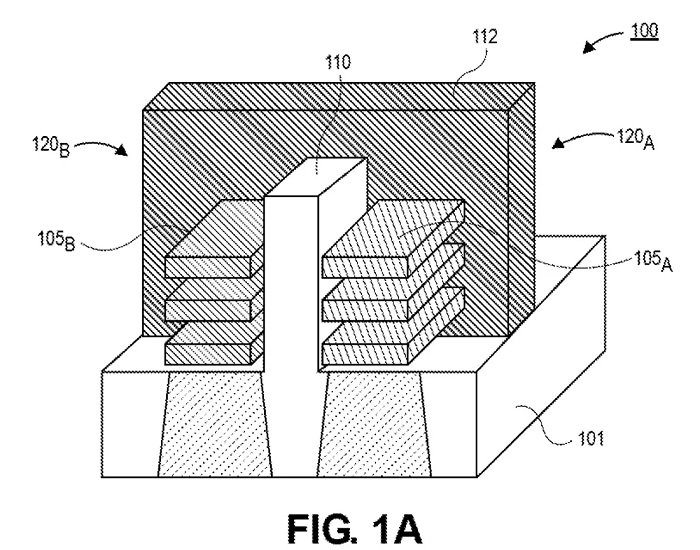

该专利全称“堆叠叉片式晶体管(stacked forksheet transistors)”技术。该专利并没有提供太多的细节,而且英特尔也没有提供PPA(功率性能面积)的改进数据作为参考。

根据英特尔方面的介绍,“这项专利描述了纳米带晶体管和锗薄膜的使用,后者将充当电介质隔离墙,在每个垂直堆叠的晶体管层中重复,最终取决于有多少个晶体管被相互堆叠在一起。这种新的晶体管设计最终可以实现3D和垂直堆叠的CMOS架构,与目前最先进的三栅极晶体管相比,该架构允许增加晶体管的数量。”

简单来说,这全新的结构目的是为了进一步缩小晶体管,同时在半导体堆叠时将特征尺寸最小化。在新的结构下,PMOS和NMOS这两种晶体管将更紧密地封装到一起,而不会影响它们的运行。如果一切顺利,基础CMOS器件的占地面积至少减半,从而让集成电路的密度轻松翻倍。但正如前面所说,由于没有提供更多细节,这种新结构在制造复杂性上将面临很大的挑战。

近些年,面对AMD等竞品的挑战,英特尔方面也开始大动作不断,先是推出口碑较好的12代Alder Lake处理器,紧接着又宣布重回芯片制造领域。此次推出新专利也是意图在芯片代工领域有所收获。

除了英特尔以外,台积电与三星已经在2nm工艺有所进展,两家芯片巨头均希望使用nanosheet/nanowire(纳米片/纳米线)晶体管结构取代目前主流的FinFET工艺。从晶体管模型来看,英特尔的结构似乎可以容纳更多的晶体管,但设计思路上其实大同小异——将半导体材料像积木一样堆叠起来。

但并不是所有的专利都能够成为实际的产品或制造技术,目前来看,英特尔这项专利想实现的难度还是过大。

最后,记得关注微信公众号:镁客网(im2maker),更多干货在等你!

硬科技产业媒体

关注技术驱动创新

AMDFinFET工艺MO处理器英特尔

AMDFinFET工艺MO处理器英特尔

微信ID:im2maker

微信ID:im2maker 长按识别二维码关注

长按识别二维码关注