半导体产业纷争下,晶圆厂一边赚钱,一边焦虑

摩尔定律“失效”必然引发“混战”,晶圆与设计、封装之间重新磨合不可避免。

最近半导体先进工艺的争夺战可以说是愈演愈烈。

日前,三星在美国SFF晶圆代工论坛上发布了新一代逻辑工艺路线图,暗示其2021年要量产3nm工艺,以压制台积电彼时的5nm工艺。在其之后不到一个月,台积电就官方宣布正式启动2nm工艺研发,不失为有力回应。

7nm,5nm,3nm,2nm...

如同开了外挂一般,不声不响,神仙打架的一招一式都是互不相让,亦精彩纷呈,让观者目不暇接。

对摩尔定律的焦虑:半导体工艺真的到极限了?

不得不说,不去看这两家各自打得如何激烈,仅这场架的行为本身传达出的信号就着实让人有些摸不着头脑。一反外界的悲观态势,晶圆制造厂发展势头迅猛且毫无畏惧,这在当下多少有些反常。

目前,一颗芯片上至少有数亿个晶体管,nm单位可以简单看成是单个晶体管尺寸大小。按照摩尔定律,随着晶体管尺寸越来越小,理论上相同大小的处理器性能会有显著提升,同时功耗相对会降低。因此某种程度上,半导体工艺的发展与产业整体成长紧密相关。

有数据显示,1987年左右,半导体产业成长率高达40~50%,到了1990年代全球半导体产业的成长率在15%~16%,但到了2000年后,全球半导体产业成长率只有4%~5%,而后随着工艺逼近个位数量级,晶圆制造因制程带来的红利也似乎已经走到尽头。

因此2018年,整个半导体产业对制程上的担忧是明显的,“半导体工艺到达物理极限”言论一度甚嚣尘上,摩尔定律失效也成为诸多半导体人口中惯常的论调。

当时,张忠谋曾站出来辟过一次谣,称半导体工艺距离物理极限还有8—10年,而延续摩尔定律的另一条路是在封装工艺上发力,即向上堆叠。言下之意,张忠谋认为短期内半导体产业的利润点不会因工艺存在大幅下跌,未来并没有那么悲观。后来任正非在谈到这一点时,也表示解决的方法比较多,未来新的技术也将能够保持整个行业的成长活力。至此,无法跟上摩尔定律带来的焦虑才稍减半分。

回顾历史,因将集成度与晶体管价格描述为反比关系,摩尔定律一直是描述半导体产业经济学效益的一种推测手段,但作为对发展趋势的分析预测理论,摩尔定律也是在质疑与自我验证中徘徊发展。

最为显著的预测是在晶圆制造上,摩尔定律认为在制程技术不断进步的前提下,每隔18个月,IC的产量将提升一倍,换个角度来看,其成本将降低50%。因至关重要,人们对制程工艺的关心和怀疑也没有减弱过。因此当半导体芯片主流制程技术为90nm时,有人认为45nm将成为物理极限;当制程技术达到45nm时,有的观点认为22nm将成为极限;而此前7nm也一度被认为是半导体工艺的极限。

容易发现,类似我们当下对能够看见的物理极限2nm甚至1nm产生怀疑与担忧一般,整个产业的情绪其实早就反复出现。因此在2018年整个产业悲观声音之下,仍然有业内人士认为,这份因“数字”变化带来的焦虑有其合理之处,却也不尽然。

从IDM到Foundry,技术驱动晶圆制造产业发展

提到nm工艺,绕不开Intel、三星与台积电这三家在先进工艺上有着卓越贡献的公司。作为先进制程工艺的代言人们,Intel是唯一活跃在公众面前的传统IDM公司,三星的工厂则与台积电一样,承接Foundry业务。

作为奠定近年半导体工艺发展的厂商之一,自10nm之后与三星、台积电之战中“败”下阵来,Intel一直在努力调整以使其主要制程工艺技术走上正轨。但是即便在市场中落败,作为曾经的工艺界大牛,Intel对整个产业的贡献是卓越的。

22nm是半导体工艺发展史上的一个关键节点,也是从此开始,胡正明发明的SOI和FinFET工艺在市场上走向了对立面,因为Intel在众人一筹莫展之际,率先在硅上做成了22nm制程FinFET,缩小了器件尺寸,成功延续了摩尔定律的生命,也将IBM、AMD等一众巨头踩在了脚下,同时将SOI工艺的支持者们远远抛在了后面。

风光无限,Intel引来众多追随者,台积电就是其中一名。但随着产业发展,14nm,10nm...晶体管越做越小,Intel也未曾料到,有一天会在7nm上栽跟头。

在近代工艺的发展历史上,7nm绝对是最受关注的工艺水平之一,很多在10nm工艺上大放异彩的半导体公司都在7nm上吃了苦头,Intel也不例外。也因此,台积电借势一举打下了大半市场,完成了自己从追随者到引领者的身份蜕变,树立了自己的定位,拿下了高通、华为等多家主流手机公司的大单。发展至今,7nm工艺给台积电带来的营收都依然占据很大比例,如2019 Q1财报显示,台积电7nm工艺营收占据整个公司营收的22%,占比最高。

图 | 台积电2019 Q1财报

与台积电稍有不同的是,这一路上三星的路走得就“绚烂多姿”许多。虽然一度被Intel怼其nm级工艺标识有夸大之嫌,但借着7nm之战,三星还是挤掉了Intel,成功上位并拿下了台积电剩余的市场份额,也成为现如今唯一被认为能够与台积电对抗的企业。

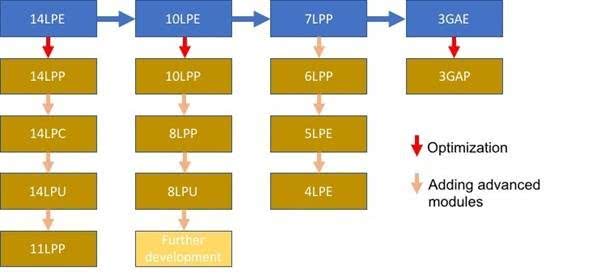

上个月,为了展现自己在制程工艺的布局,三星对外公布了其工艺路线图,一眼看过去着实让人眼花缭乱。

图 | 三星工艺路线图

不难发现,三星在3nm节点处其实已经开始放弃FinFET工艺,转向GAA晶体管。关于GAA晶体管,我们后面再做介绍。

晶圆制程工艺遭瓶颈,SOI是关键破局工艺?

首先来说三星要放弃继续研发FinFET工艺转而探索新方向这件事。其实不仅仅是三星放弃在FinFET继续研发,台积电、Global Foundries等公司也同样意识到这一工艺的局限性,尤其是该工艺相对较高的成本。因此最近一段时间内,曾因FinFET得势而被冷落的SOI工艺再度被推上风口浪尖,被认为是替代FinFET工艺带来新增长力的技术备选之一。

说起FinFET和SOI,这两项工艺其实由同一团队——前台积电首席技术官和伯克利公司的前任教授胡正明及其团队研发而出,他于1999年提出了FinFET的概念并在2000年提出了UTB-SOI(FD SOI)。这两种结构的主要结构都是薄体,因此栅极电容更接近整个通道,本体很薄,大约在10nm以下,所以没有离栅极很远的泄漏路径,栅极可有效控制泄漏,都可商用。

与SOI相比,市场主流的FinFET技术具有更高的驱动电流,且在FinFET中,应变技术可用于增加载流子迁移率。但是FinFET为人所诟病的就是其复杂的制造工艺,一手将FinFET推向市场的Intel曾称,SOI晶圆占总工艺成本的10%左右,比体硅增长2-3%。

而由于SOI技术非常接近平面体硅技术,现有的bulk技术库可以轻松地转换为SOI库,采用SOI技术成本就低许多。且与FinFET相比,SOI的另一个优点就是功耗低。不过SOI技术有其局限性,突出的两点就是采用其比较难控制整个晶圆上的锡硅膜且当时它的支持厂商少。

因此2012年英特尔在Ivy-Bridge处理器的22nm节点推出了Trigate FET后,主流晶圆厂包括台积电、Global Foundries和三星在内都纷纷求稳,站队FinFET。

不过也有少数厂商不甘于从大势,当时与Intel发布同年,意法半导体在28nm技术上发布了其首款用于移动处理器的FD-SOI芯片,宣布站队FD-SOI技术,但是因成果明显处于弱势,提供技术支持的厂商相对则少了许多,其中有被Intel打败的IBM。

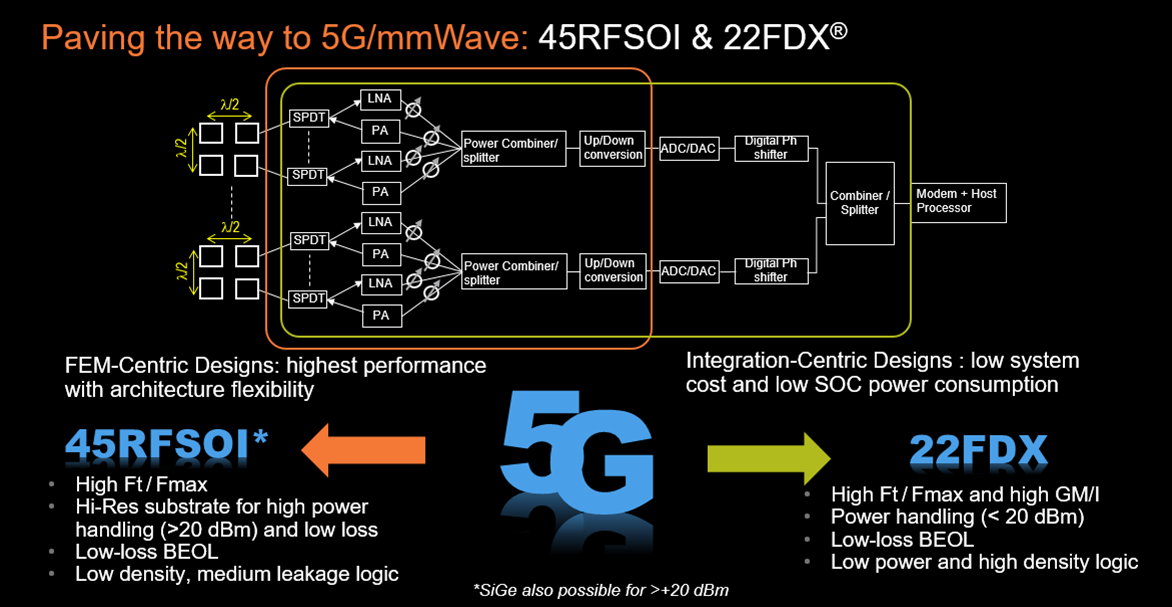

发展至今,除了IBM,Global Foundries、三星、中芯国际、Soitec等诸多厂商都开始支持SOI技术,且随着物联网、5G等领域发展对功耗的强需求以及SOI技术在射频领域的成功应用,SOI技术又再次被提上日程,因此得到了大力发展。

图 | 格芯在SOI上的解决方案

很多人认为SOI是未来替代FinFET技术的未来工艺,但是亦有诸多人表示SOI与FinFET本出自同门,最终应当会殊途同归甚至以融合形式出现,无法翻出大浪甚至改变半导体制程工艺走到尽头的现状。因此这时,我们就能理解为什么三星在3nm之后走向了GAA晶体管。

工艺不行,晶体管来战

开篇提到过,晶体管尺寸减小可以直接使芯片性能得到提升,但是当工艺达到一定程度无法带来更进一步优化时,诸多晶圆厂和不同领域的芯片公司巨头们自然就会想到去优化单个晶体管以提升芯片整体性能。三星看重的就是这一点。

GAA晶体管,又称环绕式闸极纳米线晶体管,也曾被认为是突破现有工艺的候选技术之一。因为GAA晶体管拥有高静电掌控能力,可以实现CMOS微缩,在水平配置中,也是目前主流FinFET技术的自然延伸,可以通过垂直堆叠多条水平纳米线来最大化每个覆盖区的驱动电流。

从商业化角度来看,GAA晶体管技术因“延续”当下的工艺技术,偏于保守也更易实现。作为GAA晶体管技术的最大推崇者,三星就在前段时间的SFF美国分会上表示,公司计划在2021年推出一款突破性的产品,这款产品基于三星3nm GAA(gate all around)工艺制造,性能提高35%,并将功耗降低50%、芯片面积缩小45%。如若真能如此,该技术的采用确实能够带来显著改进。

当然除了三星力推的GAA晶体管,在特定的通信和电源领域,也已经有诸多厂商开始采用GaN(氮化镓)晶体管来设计芯片,以撼动现有硅晶体管的主流地位。

图 | 基于GaN的设计

与Si等效材料相比,GaN晶体管具有更优秀的成本效益,这将使得GaN器件的应用从大型工业设备到小型化的手持设备都具有吸引力。尤其在电源芯片领域,GaN材料的卓越性能表现已经在技术上碾压了硅材料。

谈到5nm+之后的工艺规划时候,台积电也表示他们在储备纳米线(GAA)等先进晶体管结构和High Mobility Channel、Ge和2D材料的技术。他们同时还创新性提到了新型low—k材料,在他们看来,这些将会是未来半导体工艺演进的关键支撑。

虽然目前主流晶圆厂在力保市场的稳定,但从工艺发展百花齐放的态势去看,不确定性已经在急剧加大,接下来的纷争是免不了了。

全产线提升性能,纷争之下力延摩尔定律

如张忠谋曾提到的,为延续摩尔定律,先进封装也是晶圆厂接下来可走的路。因此现如今除了密切关注上述能够“撼动根本”的新技术动态之外,在产业链上下功夫也是晶圆厂首选的保守改革之路,且容易实现。

以台积电为例,他们最近就在台积电2019中国技术论坛上谈到了这一方面,它表示,在封装方面,台积电已经有所准备,如他们已经陆续推出CoWoS(Chip on Wafer on Substrate)、bumping、InFO(Integrated Fan-Out)等后端3D封装产品和前道3D封装工艺SOIC(system-on-integrated-chips)和全新的多晶圆堆叠(WoW,Wafer-on-Wafer)。而为了验证其在先进工艺上的研究成果,最近台积电甚至利用先进封装和互联技术设计了一款基于7nm的小芯片This,性能表现也是喜人。

图 | This结构图

当然,除了如台积电一般,晶圆厂开始融合一部分封装工序以减低成本,全产业链软硬件协同融合设计芯片也成为降低芯片成本的一种手段,以延续摩尔定律。

不管怎样,无论是设计公司,还是晶圆厂,其最终目的都是力延半导体产业的摩尔定律,最大程度保证整个产业的发展活力和盈利空间,因此虽然技术给整个产业链带来动荡,各家之争的最终目的却是一致的,只看谁能C道出位了。

最后,记得关注微信公众号:镁客网(im2maker),更多干货在等你!

硬科技产业媒体

关注技术驱动创新

性能硬件纳米芯片软硬件

性能硬件纳米芯片软硬件

微信ID:im2maker

微信ID:im2maker 长按识别二维码关注

长按识别二维码关注